分類:ハーネスアセンブリ

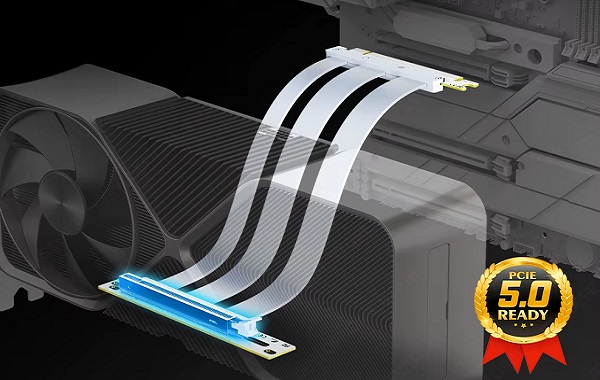

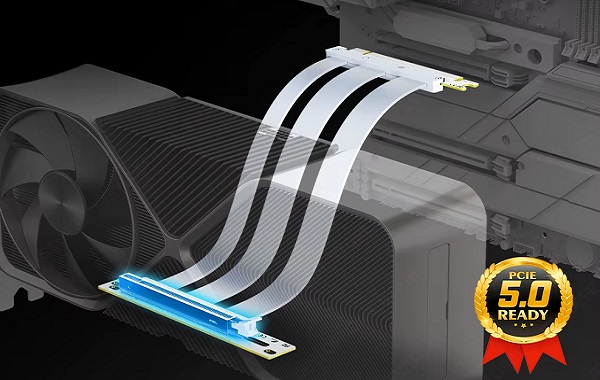

PCIe標準は、Gen3の8GT/sからGen5の32GT/sに速やかに進化し、Gen6の64GT/sの高速段階に入っています。伝送速度の大幅な向上に伴い、チャネル損耗、抵抗制御、干渉耐性が非常に高い要求されています。高速信号の品質を保つために小さなスペースで、極細同軸線束(Micro Coax)がその高い遮蔽構造と柔軟な配線能力により、高速接続をサポートする新たな選択肢として注目されています。

本文は構造特性、高速挑戦、そして応用可能性の三つの視点から分析を行う。

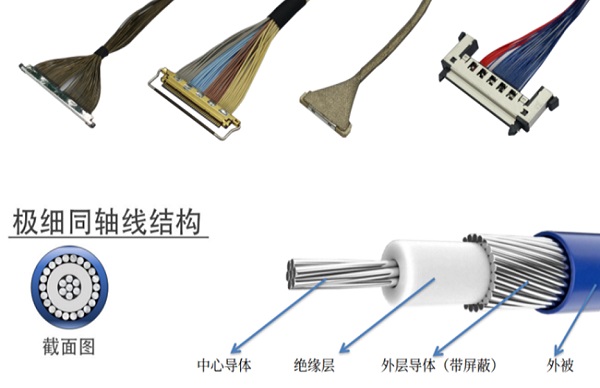

一、極細同軸線束の構造特徴

極細同軸線束は一般的にAWG36~40などの細い線径を使用しており、内导体、絶縁層、屏蔽層、および外被覆で構成されています。同軸構造は優れた電磁遮蔽効果を提供し、ノイズと干渉を効果的に低減します。その柔軟性により、複雑なレイアウトに適応し、空間が限られている場合や迂回が必要なデザインに有利です。線束全体が軽量で小さく、小型化、高密度モジュールの内部高速信号接続に適しています。厳しい環境下での高速伝送に柔軟な経路選択を提供します。

二、PCIe Gen5/Gen6の高速伝送の課題

リンク速度が32–64GT/sに向上するにつれて、チャネル損耗とインピーダンスの一致性がシステム性能に影響を与える重要な要因となります。高速伝送は低いインサーション損耗、低い反射、そして安定した差分インピーダンスに非常に高い要求をかけています。どんな過度な曲がりや線径の違いも信号の減衰を引き起こす可能性があります。多チャネルが同時に動作する場合の交叉ノイズ、モード変換、そしてノイズのカップリングもより顕著になります。したがって、接続媒体には高品質なシールド能力と優れた電気的安定性を持ち、システムの均衡戦略と組み合わせて、目の形の開口度と誤り率の性能を保証する必要があります。

三、Micro Coax が PCIe に適用される可能性と設計の重点

極細同軸線束は、高速遮蔽能力、低い交叉干渉、そして柔軟な配線において明確な利点を持ち、基板間やモジュール間の高速伝送ニーズに適応できます。線径が細いため、高い周波数領域での信号損耗がより敏感になるため、線束の経路をできるだけ短くし、過度な曲げを避け、および屏蔽層の接地設計の安定性と信頼性を確保する必要があります。設計プロセスでは、Sパラメータの分析、眼図のシミュレーション、および実際のリンクテストが必要であり、これにより、全体のチャネルが高い周波数条件下でも制御可能な損耗、低いジャitter、および高い一貫性を持ち続けることが確保されます。大量生産の一致性、線束の幾何学的構造の安定性、および屏蔽の完全性も、性能を決定する重要な要素です。

全体として、極細同軸線束は構造の柔軟性、高い遮蔽特性、高密度設計への適応において明らかな利点を持ち、PCIe Gen5/Gen6の実行可能な接続方案として考慮されます。素材の品質、遮蔽の完全性、加工の一致性、完全な信号シミュレーション検証を確保する前提下、Micro Coaxは高速リンクでの損耗管理と干渉抵抗要求を満たすことができ、次世代高速デバイスに信頼性の高い内部接続方法を提供します。もしインピーダンス制御、損耗管理、構造の安定性に注意を払わない場合、性能問題として眼図の収縮や誤码の増加が引き起こされる可能性があります。

わたしは【蘇州瑞成元電子テクノロジー】,長期専念高速信号ラインケーブルと極細同軸線ケーブルのデザインとカスタマイズ、お客様に安定信頼性の高い高速接続ソリューションを提供いたします。相談やカスタマイズサービスをご希望の方はお気軽にご連絡ください。尹経理:18913280527(ラインも同じです)。